Free Model Foundry was founded by board designers for board designers. We had verification problems that were not being addressed to our satisfaction by the semiconductor companies. The EDA industry made an effort through Logic Automation and some proprietary libraries but, their business models prevented them from providing what we needed.

What we needed was:

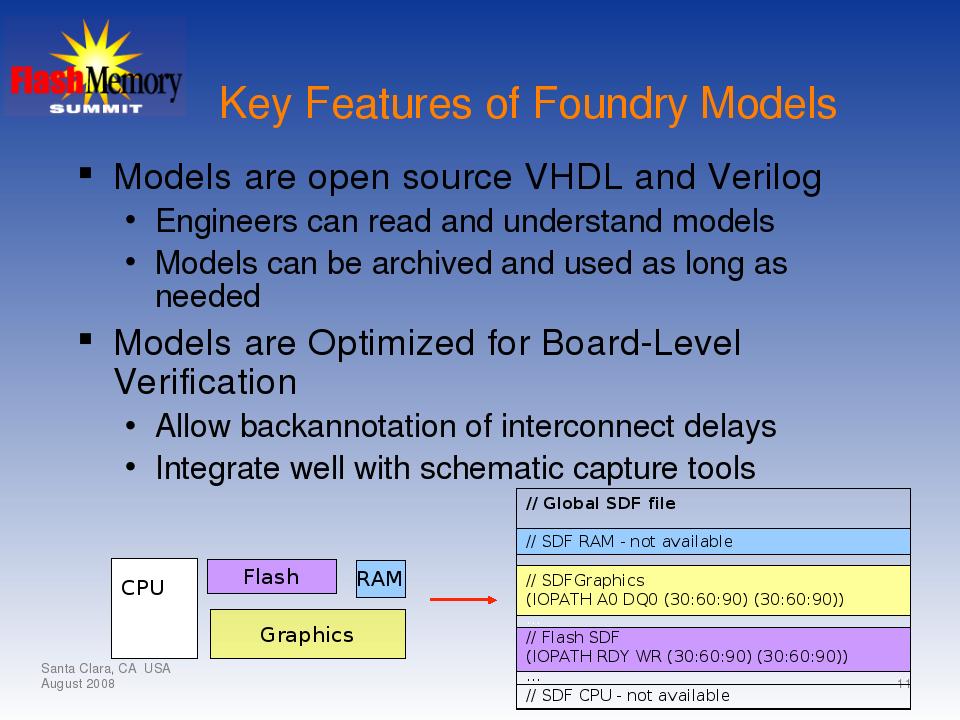

- Models we could read. When a simulation reports errors, the engineer needs to determine whether he misunderstood how the component works; connected it incorrectly; or, found a bug in the model. He cannot do this with encrypted models.

- Models we could keep indefinitely. We were in a mil/aero environment. It was common for projects to be resurrected after 20 years. Compiled models that required licensing software cannot be counted upon to be usable 5 years in the future much less 20.

- Vendor independence. Even if you have a simulator you like from a profitable vendor you think is wonderful, there is no guarantee that tool will be available next year. Models must be portable which means they must conform to industry standards.

The conclusion was we had to have open source VHDL and/or Verilog models. We also concluded that the models must be written in a style that facilitated board design.

These requirements are:

- Model must integrate well with schematic capture tools. This includes having the ports on the models match the pins on the schematic symbol. Most boards are still designed with schematics. Schematic capture tools are capable of generating VHDL/Verilog netlists that match the netlists going to PCB layout. The writing a simulation netlist that does not match the layout is tedious and in effective.

- A method must be provided for backannotating interconnect delays from the layout tool to the simulator. We chose an existing standard, Standard Delay Format (SDF). Many PCB tools can generate an SDF file that maps to the simulation netlist.

Meeting the above requirements brought additional advantages.

We were able to write models at higher levels of abstraction then were generally used. The result was more readable models and much faster simulations. The models are, of course, non-synthesizable but that just make them easier to justify by the IC manufacturers.

Having defined the nature of the simulation models, we needed to work out a business model. Since we distribute the model source code, we cannot expect to charge the end users. We decided to charge only for model creation. We get paid only once for each model by the requester. After that, the models are made freely available to design engineers.

If the requester is the manufacturer, as we prefer, the models help customer engineers design the components into systems faster and with fewer board spins, accelerating the customer’s time to volume purchases. They also allow the engineer to answer many of their own questions, reducing the load on the manufacturer’s applications engineers.